Parallel Input Serial Output Shift Register Vhdl Code

12.09.2019

Download and install xender. 74F675A 16-Bit Serial-In, Serial/Parallel-Out Shift Register 74F675A 16-Bit Serial-In, Serial/Parallel-Out Shift Register General Description The 74F675A contains a 16-bit serial in/serial out shift reg-ister and a 16-bit parallel out storage register. Separate serial input and output pins are provided for expansion to longer words.

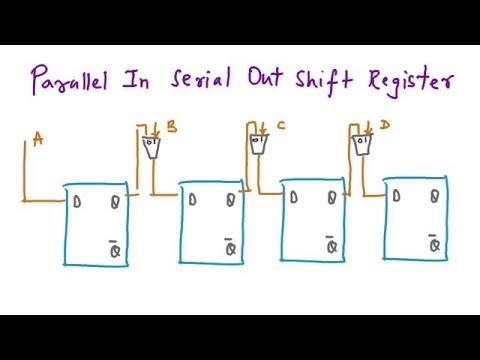

Design of Parallel IN - Serial OUT Shift Register using Behavior Modeling Style -| Output Waveform : Parallel IN - Serial OUT Shift Register |

VHDL Code-

-------------------------------------------------------------------------------

--

-- Title : parallel_in_serial_out

-- Design : vhdl_upload2

-- Author : Naresh Singh Dobal

-- Company : nsdobal@gmail.com

-- VHDL Programs & Exercise with Naresh Singh Dobal.

--

-------------------------------------------------------------------------------

--

-- File : Parallel IN - Serial OUT Shift Register.vhd

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity parallel_in_serial_out is

port(

clk : in STD_LOGIC;

reset : in STD_LOGIC;

load : in STD_LOGIC;

din : in STD_LOGIC_VECTOR(3 downto 0);

dout : out STD_LOGIC

);

end parallel_in_serial_out;

architecture piso_arc of parallel_in_serial_out is

begin

piso : process (clk,reset,load,din) is

variable temp : std_logic_vector (din'range);

begin

if (reset='1') then

if (reset='1') thentemp := (others=>'0');

elsif (load='1') then

temp := din ;

elsif (rising_edge (clk)) then

dout <= temp(3);

temp := temp(2 downto 0) & '0';

end if;

end process piso;

Serial In Parallel Out Shift Register Vhdl Code

end piso_arc;Comments are closed.